본 글은 2022년 6월 7일 발행된 미래에셋증권의 반도체 리포트를 공부목적으로 정리 요약한 글입니다.

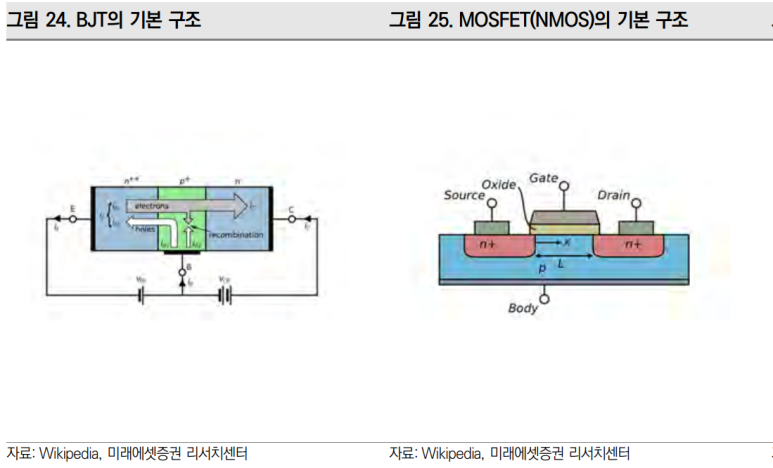

트랜지스터

트랜지스터는 전자회로 내에 전기신호의 증폭과 스위칭을 담당하는 소자

BJT(접합형 트랜지스터), FET(전계효과 트랜지스터) 구분

FET는 게이트 전극에 전압을 건 뒤 채널의 전기장에 의해 전류를 제어하는 트랜지스터, 고밀도 집적에 유리한 구조, 현대 IC의 주류

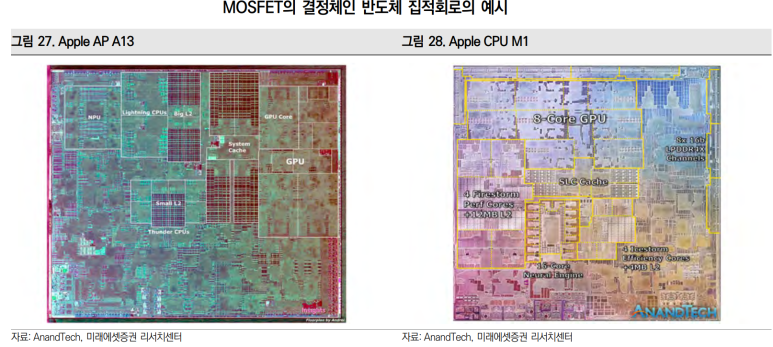

MOSFET

금속 산화막 반도체 전계효과 트랜지스터(Metal Oxide Semiconductor Field Effect Transistor)의 약자로 FET의 일종

MOSFET은 N형 반도체나, P형 반도체 재료의 채널로 구성되어 있고, 재료에 따라서 NMOSFET, PMOSFET, 두 가지를 모두 가진 CMOSFET으로 구분

CMOS는 개별로 회로를 구성할 때 보다 소비전력 낮고, 회로 단순화

대부분의 로직반도체는 CMOS 기반으로 회로 구성

좋은 CMOS 반도체 조건

트랜지스터로 구현된 모든 회로는 입력신호와 출력신호 사이의 시간차이 존재

Delay가 크다는 것은 회로의 속도가 느리다는 것을 의미하며 이를 줄이는 것이 중요

작게 만들면서 생산성 급격히 증가, 다만 Channel의 길이가 100nm에 이르러서 스케일링만으로 전류의 크기 개선할 수 없게 되어짐

소자 성능을 개선하기 위한 방법들

Uni axial strain을 이용한 Mobility 개선

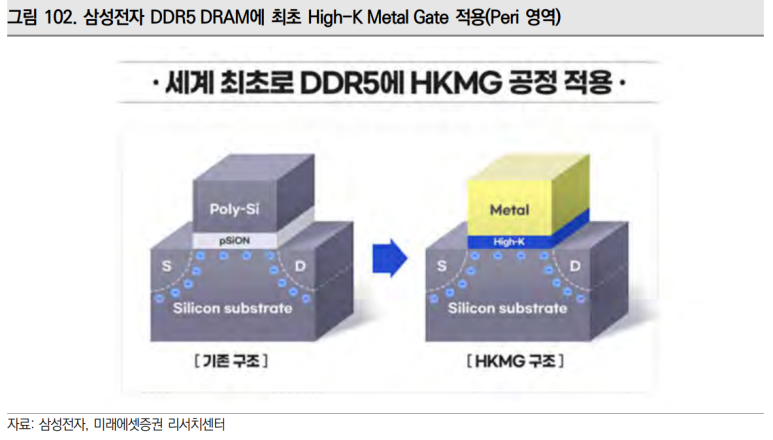

High-K Metal Gate를 적용해 Capacitance(정전용량)의 향상

Fin FEt, GAAFET 등 소자의 구조 변경을 통한 성능 개선

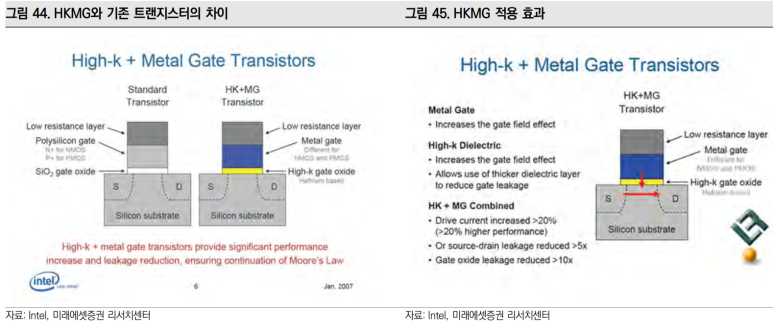

High-K Gate

MOSFET의 스케일링 지속되며 Gate와 채널사이 산화막의 면적이 줄어들게 됨

면적이 줄어드는 가운데 산화막의 Capatance(정전용량)을 줄이기 위해 산화막의 TOX를 줄여야 함

결국 SiO2보다 유전율이 높은 HfO2로 유전막 변경

HfO2는 유전상수 20으로 High-K 물질

이로 인해 Logic 반도체 공정에 ALD 도입

Matel Gate

최초의 MOSFET은 100nm까지 Metal Gate를 사용했으나 Metal의 녹는점이 낮아 공정을 거듭하면서 녹아버리는 일 발생

이러한 이슈를 제거하기 위해 High-K 유전막과 Metal Gate를 통칭해 HKMG구조라고 함

인텔은 HKMG구조를 2007년 적용해 45nm기반 CPU 발표

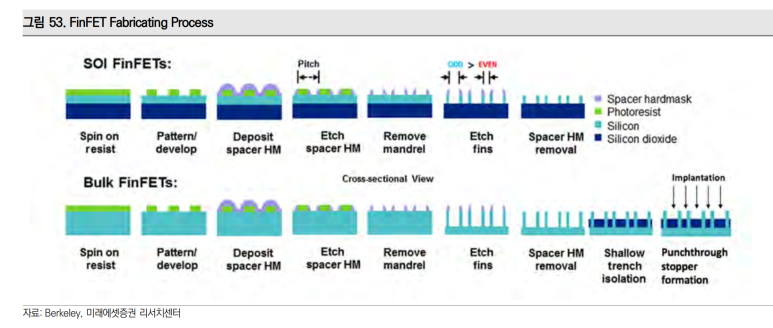

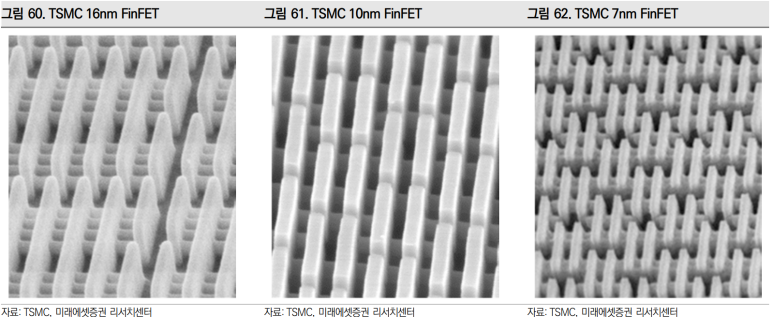

FinFET

2차원적인 스케일링이 거듭되면서 기존 트렌지스터 구조로는 SCE(Short Channel Effect)를 감당 불가

SCE : 채널간의 길이가 짧아지면서 이런저런 문제발생(제어불가)

그로인해 채널의 3면을 감싸는 FinFET 구조 개발

핀펫 공정의 적용으로 인해 Patterning 및 Deposition장비 수요 증가

TSMC 2014년 FinFET구조 도입, 삼성전자 2015년 도입

현재 FinFET 이후 공정공급이 가능한 파운더리는 4개사(TSMC, 삼성전자, SMIC, 글로벌파운더리)

생산이 가능한 업체는 Intel, TSMC, 삼성전자

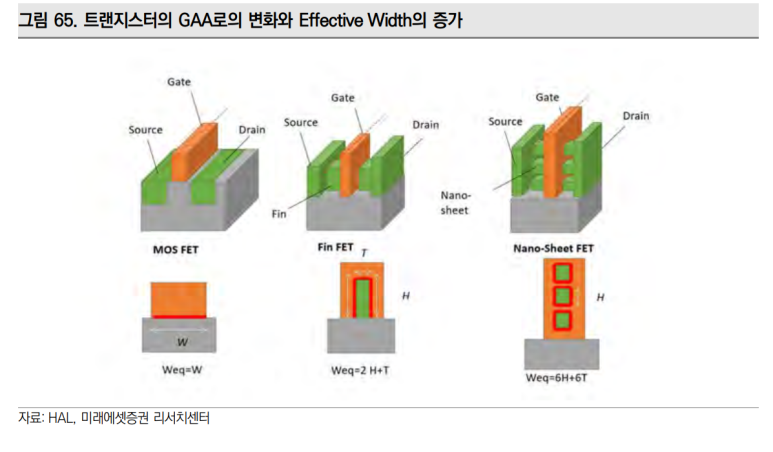

GAAFET

FinFET구조에서도 소자의 미세화가 계속되면서 구조의 한계가 드러남

5nm수준에 이르자 SCE 허용범위 넘어섬

Fin의 종횡비(Aspect Ratio)가 증가하면서 저항 증가

그 이후 등장한게 GAA(Gate All Around)

GAA는 Gate가 채널의 4면을 둘러싸고 있기에 Gate의 통제력을 한층 더 높일 수 있음

Si/Sige Sheet Epitaxy 수요 증가

Sige에 대한 고선택비 Selective Etching 장비 수요 증가

ALD 공정 수요 증가

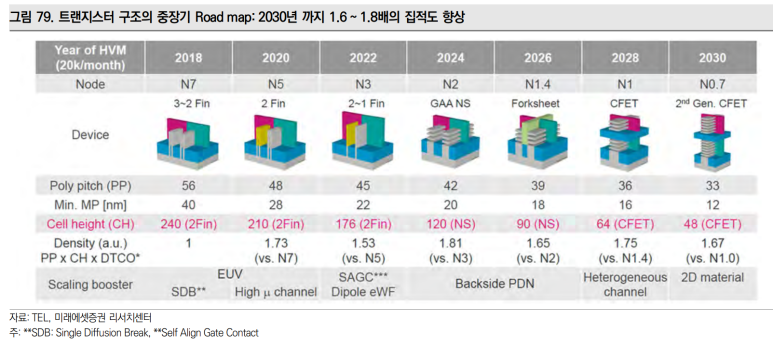

TSMC는 24년말부터 GAA기반 N2 양산 투입 계획

22년말 N3 웨이퍼 투입(주요 고객사, 애플과 인텔)

N2 주요 고객사는 애플 아이폰 16향 AP

삼성전자 22년 하반기부터 GAA기반 3nm 양산 시작

인텔은 24년 상반기부터 2nm RibbongFET 공정 적용(MBCFET 유사구조)

트랜지스터 구조 FinFET -> GAAFET

전반적인 공정 Step수 증가

뚜렷하게 증가하는 공정은 ALD, Etching, Epitaxy

속도가 중요한 LOGIC에는 Epitaxy를 통해 결정질 Si의 적층이 필수

ALD 수요 증가 : GAA구조에서는 Nano Wire 표면에 High-K 유전막 증착뿐만아니라 Metal Gate 물질 증착을 위해서라도 Step Coverage가 높은 ALD 필수

Selective Etching 수요 증가

Wet Etching : 염산(HCI)를 이용하거나 HF/H2O2/H2O 희석액을 이용한 습식식각 유력

HF, H2O2는 솔브레인과 한솔케미칼 수혜 기대

Dry Etching : Sige과 Si층을 O2플라즈마로 산화시킨다음 SigeO만 에칭하고 다시 Sige를 산화시키고 식각하기를 반복하는 방식

관련 장비는 램리서치와 어플라이드머트리얼즈 위주로 공급될 예정

EUV 관련 밸류체인

파운드리 업체들의 본격적인 EUV 기반 생산경쟁은 1년도 남지 않음

에스엔에스텍(블랭크마스크, 펠리클)

에프에스티(펠리클)

파크시스템스(AFM 장비)

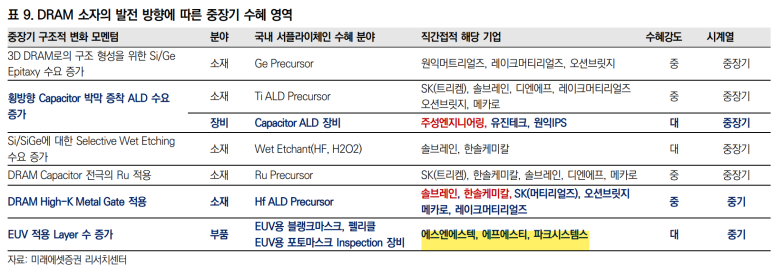

3D DRAM

3D DRAM의 경우 적층의 방식이 Si/SiGe Epitaxy를 이용한 단결정 적층방식이 될 가능성이 높음

HF/H2O2/CH3COOH를 이용한 습식 식각박싱이 유력

HF, H2O2는 솔브레인과 한솔케미칼 주력 사업분야

DRAM

DRAM(Dynamic Random Access Memory) : 임의적으로 접근이 가능하다는 의미로 원하는 위치에서 원하는 데이터를 바로 읽거나 쓸 수 있다는 의미

DRAM과 SRAM으로 분류되지만 속도는 SRAM이 빠르고 단가가 비싸서 CPU, AP 캐시메모리 위주로 사용

일반적인 PC에서는 DRAM이 대중적으로 사용

Capacitance는 CAP의 면적과 유전율에 비례, 두께 반비례

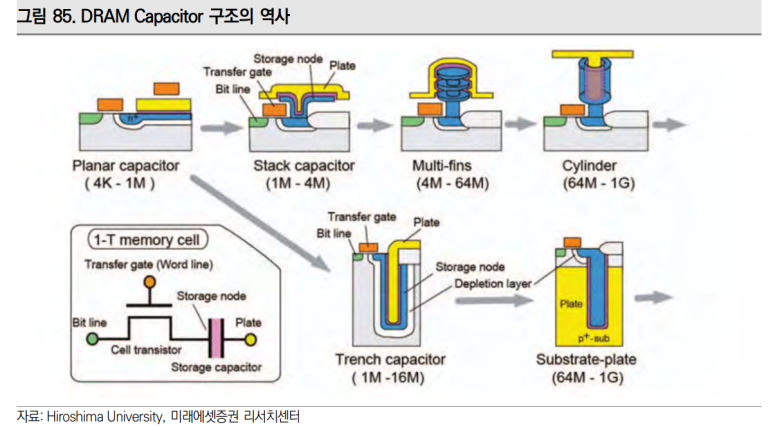

과거 DRAM업체들이 STACK(쌓기)과 TRENCH(파기)의 기로에서 유럽은 TRENCH, 일본과 삼성은 STACK방식 채택

MESH(Mechanically Enhanced Storage node for virtually unlimited Height): Capacitor의 Apspect Ratio로 인한 쓰러짐을 방지하기 위한 지지대를 형성하는 공정

최신 DRAM에서는 Mesh ring이 최소 3개 Layer 사용

유전율이 크면서 누설전류를 억제할 수 있는 물질을 찾는 것이 앞으로 DRAM 성능을 개성할 수 있는 소재의 핵심요소

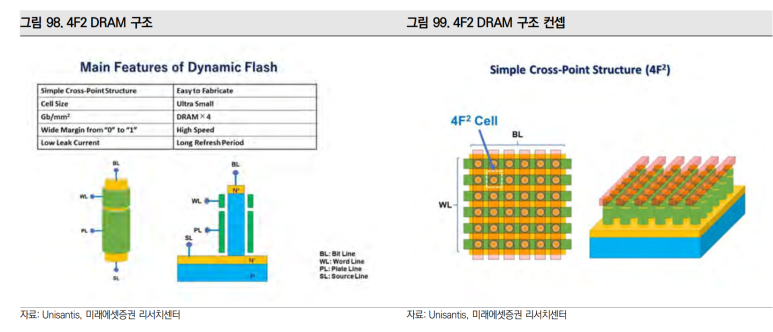

4F2 DRAM : 현재 DRAM Cell Transistor, Source, Gate, Drain이 가로로 배치된 구조를 세로로 배치해 전체면적을 1/4가까이 줄이는 방식

3D DRAM : 25년 이후에 Gate를 수직으로 적층하고, Capacitor를 횡방향으로 나열하는 3D DRAM에 대한 논의가 학계와 산업계에서 진행중

글로벌 장비사들의 제시하는 차세대 DRAM도 3D DRAM

Si/Sige 장비의 경우 어플라이드 머트리얼즈와 ASMI가 독점

국내는 유진테크, 주성엔지니어링 장비 보유하고있느나 양산 한계

3D DRAM에서 Capacitor의 유전체 증착을 위한 ALD 수요 증가(원익IPS, 유진테크, 주성엔지니어링 등)

DRAM Capacitor 소재 벨류체인 Zr(지르코늄)

일본 Adeka, SK트리켐, 메카로, 디엔에프, 레이크머트리얼즈

HKMG의 사용되는 Gate Oxide는 주로 HfO2(하프늄 옥사이드) 사용하기에 HF프리커서와 ALD 장비 필요

Logic반도체에서 50년의 반도체 역사상 두번째로 진행되는 MOSFET 구조 변화 임박

박막 증착 이후, SiGe(실리콘저마늄)를 선택적으로 제거하는 공정 추가

EUV는 Stepper 뿐만 아니라 PhotoResist, Photomask, Pelicle, Inspection 등 기존과 다른 전반적인 생태계를 조성하는 분야

3D Dram의 횡방향 Capacitor 표면의 유전체 증착을 위한 ALD 수요 또한 증가

다음편 계속

Disclaimer

- 당사의 모든 콘텐츠는 저작권법의 보호를 받은바, 무단 전재, 복사, 배포 등을 금합니다.

- 콘텐츠에 수록된 내용은 개인적인 견해로서, 당사 및 크리에이터는 그 정확성이나 완전성을 보장할 수 없습니다. 따라서 어떠한 경우에도 본 콘텐츠는 고객의 투자 결과에 대한 법적 책임소재에 대한 증빙 자료로 사용될 수 없습니다.

- 모든 콘텐츠는 외부의 부당한 압력이나 간섭없이 크리에이터의 의견이 반영되었음을 밝힙니다.